Avec CXL sur ses Xeon Sapphire Rapids, Intel pousse les serveurs composables

La 4e génération de puces Xeon Scalable d'Intel, Sapphire Rapids, taillées pour les besoins en calcul haute performance, va bénéficier comme ses prédécesseurs Ice Lake d'une finesse de gravure en 10nm SuperFIN. Des capacités mémoire à large bande passante sont ajoutées et surtout le support du protocole CXL pour aller vers des serveurs composables.

Intel ne perd pas de temps. Dans le cadre de la conférence en ligne International Supercomputing 2021, le fondeur a fait état de plusieurs annonces produits majeures pour monter d'un cran les capacités de calcul et de traitement des systèmes de calcul haute performance (HPC). La plus importante est sans aucun doute l'annonce de la 4e génération de puces Xeon Scalable, Sapphire Rapids, qui viennent épauler les modèles Ice Lake lancés il y a moins de trois mois. Attendus au premier semestre 2022, elles doivent traiter plus rapidement les workloads en modélisation et simulation, intelligence artificielle, analytique, bases de données en mémoire... Deux gammes de processeurs Sapphire Rapids seront proposées, dont une dotée de capacités mémoire à large bande passante (high bandwith memory).

Les puces Sapphire Rapids tirent partie des technologies DDR5, PCIe 5.0 et surtout du CXL 1.1 (voir encadré) pour aller vers des serveurs composables et intègrent un moteur d'accélération des traitements en intelligence artificielle. Baptisé Advanced Matrix Extensions (AMX), ce dernier doit améliorer les capacités de traitements d'apprentissage profond et d'inférences. Intel compte proposer ses Xeon Scalable Sapphire Rapids HBM aussi bien à ses clients entreprises qu'aux fournisseurs de serveurs et de systèmes HPC. A noter que cette génération de processeurs qui va donc supporter la mémoire DDR5 pourra très bien fonctionner sur une configuration système équipé de barrettes DDR4.

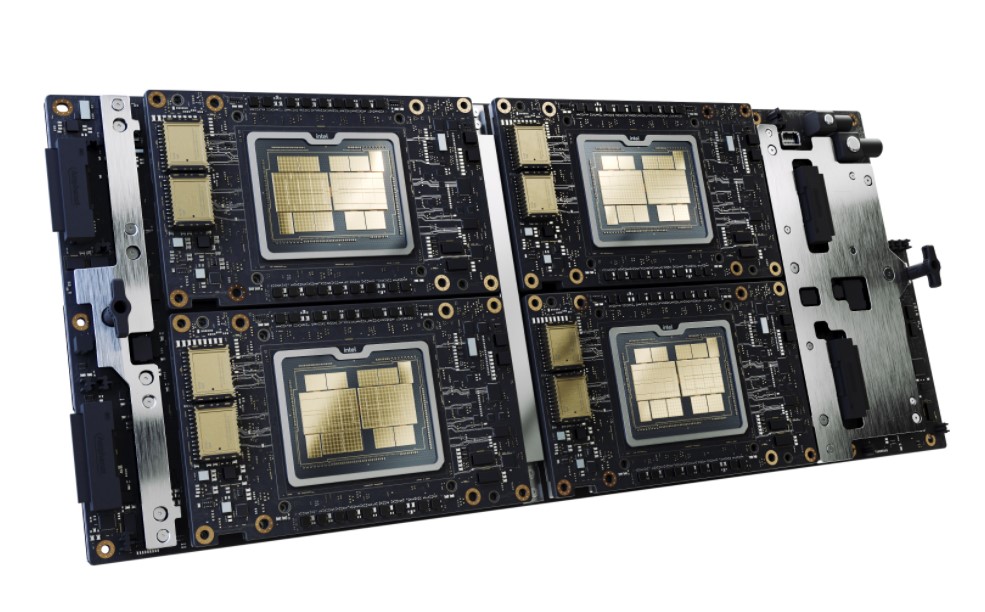

Intel a révélé que le GPU Ponte Vecchio sera disponible dans un facteur de forme OCP Accelerator Module (OAM) et un sous-système à quatre voies Intel pour répondre aux besoins des applications HPC. (crédit : Intel)

Un design processeur basé sur Golden Cove

Tout comme la 3e génération de processeurs Intel Xeon Scalable Ice Lake, Sapphire Rapids s'appuie sur une technologie de finesse de gravure 10nm SuperFIN. Rappelons qu'il s'agit de transistors FinFET améliorés dotés de condensateurs métalliques très isolants. La dernière génération de mémoire Optane d'Intel, Crow Pass, est par ailleurs également supportée. Comme évoqué depuis plusieurs mois, le design processeur (microarchitecture CPU) des Xeon Scalable Sapphire Rapids est basé sur Golden Cove afin d'améliorer en particulier l'efficience énergétique.

Intel n'a pas fourni à ce stade davantage de précisions sur les configurations et caractéristiques techniques de ses dernières puces Scalable, que ce soit en termes de capacité mémoire ou de bande passante. « Nous nous attendons à ce que la mémoire GPU par serveur atteigne jusqu'à 8 rangs de mémoire HBM2e de 16 Go chacune, avec 1 à 4 rangées bord à bord menant à 64 Go de HBM. À une vitesse maximale théorique de 460 GB/s par rangée, soit jusqu'à 1840 GB/s de bande passante, bien que nous puissions imaginer quelque chose de plus proche de 1 TB/s ce qui constituerait un accroissement considérable en termes de rendement et de performance », indique Anandtech.

Des puces Sapphire Rapids dans les supercalculateurs Aurora

Deux organismes ont déjà opté pour des supercalculateurs Aurora embarquant des systèmes dotés de processeur Sapphire Rapids, à savoir le Crossroads supercomputer du Los Alamos National Laboratory et l'Argonne National Laboratory. Ce dernier va coupler l'année prochaine deux processeurs Sapphire Rapids à 6 accélérateurs GPU Intel Ponte Vecchio qui font par ailleurs également l'objet d'annonces de la part du fondeur américain.

Intel a en effet révélé que son prochain GPU Ponte Vecchio sera disponible dans un facteur de forme OCP Accelerator Module (OAM) et un sous-système à quatre voies pour répondre aux besoins des applications HPC. Actuellement, différents modèles de GPU Xe pour systèmes HPC sont actuellement en cours de validation. « Nous avons lancé le serveur graphique Intel SG1, basé sur le Xe-LP, et nous échantillonnons le DG2, basé sur Xe-HPG sur d'autres serveurs qui sortent actuellement sur le marché. Nos produits basés sur Xe-HP sont utilisés pour l'activité Intel DevCloud », a par ailleurs précisé Trish Damkroger, responsable de l'activité HPC d'Intel.